Efficiency in memory management is not just a technical goal. It is a competitive edge, especially as devices become smaller and more power-sensitive. At the center of this pursuit is US7057960B1. This patent introduces methods to reduce power consumption during background operations in memory arrays.

InnoMemory LLC, a non-practicing entity, has filed multiple litigations asserting this patent, including ongoing cases against American Airlines, American National Bank of Texas, and others.

Rather than focus on legal proceedings, this article uses the Global Patent Search platform to explore structurally similar technologies. We examine patents that reflect the architectural concepts of US7057960B1, such as section-controlled refresh operations and periphery circuit signaling.

Whether you are in hardware research, patent analytics, or semiconductor strategy, this GPS-powered review offers a clear and data-supported look into innovations driving power-efficient memory design.

Understanding Patent US7057960B1

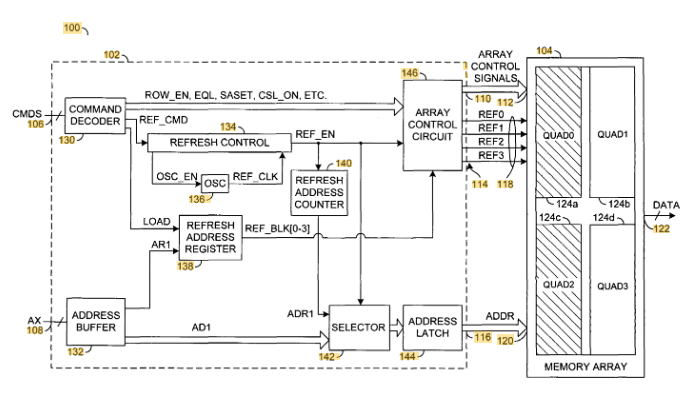

US7057960B1 introduces a method and architecture designed to reduce power consumption in memory devices, particularly during background operations like refresh cycles. The invention addresses inefficiencies in conventional DRAM refresh methods by enabling selective activation of only the necessary memory sections. It further reduces power by limiting control signal activity to sections that require refreshing. This design is especially useful in battery-powered or standby-driven applications where minimizing standby current is essential.

Source: Google Patents

Its Four Key Features Are

#1. Selective section refresh: The memory array is divided into multiple sections, and only the sections storing data to be retained are refreshed.

#2.Periphery circuit control: Periphery array circuits are activated only for sections being refreshed, minimizing unnecessary power usage.

#3. Programmable refresh logic: Control signals are generated based on programmable address inputs, allowing flexible and efficient memory refresh behavior.

#4. Support for background operations: The system supports refresh, parity checking, and other background tasks without engaging unused memory areas.

The architectural concepts described in US7057960B1 remain directly relevant when evaluating new technologies focused on power-efficient memory operation. Similar techniques around segmented access and control are explored in our review of secure data access systems like US9465913B1.

Fun Fact: Low-power design isn’t the only optimization at play. US7323982B2 demonstrates how multi-network transponders and geofencing conserve resources in fleet monitoring, echoing the efficiency themes of memory refresh.

Similar Patents As US7057960B1

To explore technologies conceptually aligned with US7057960B1, we used the Global Patent Search (GPS) tool. Below is a quick glimpse of the GPS tool in action:

Source: Global Patent Search

This analysis revealed several patents addressing selective memory refresh, low-power standby modes, and periphery circuit efficiency in memory architectures. These references provide a closer look at how similar challenges have been approached through optimized control logic and segmented array design.

For another example of component-level innovation, see how modular heating systems were handled in US9462897B2’s structural and thermal cabinet design.

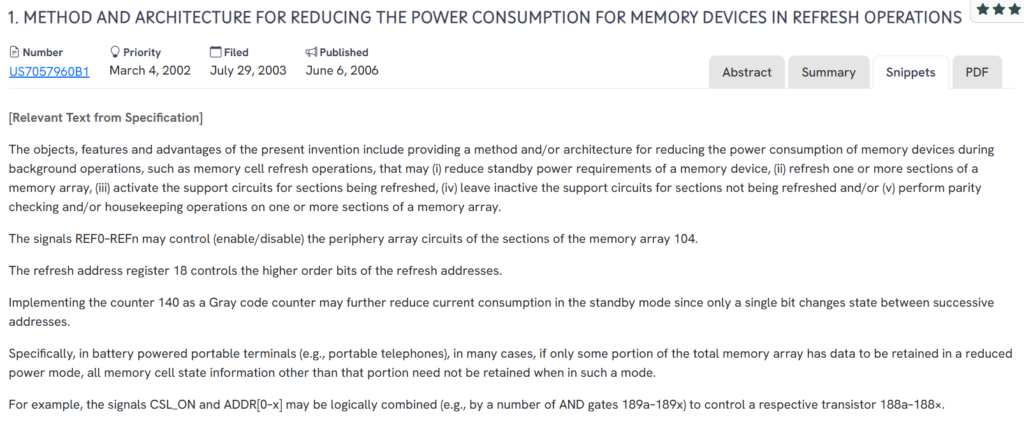

#1. US7057960B1

This U.S. patent, US7057960B1, published in 2006, introduces a power-efficient architecture for memory devices that reduces energy consumption during background operations.

Source: GPS

What This Patent Introduces To The Landscape

- Section-based refresh – Only the memory sections with critical data are refreshed during standby, avoiding unnecessary power drain.

- Periphery circuit control – Activates support circuitry only for sections undergoing refresh, keeping inactive sections fully disabled.

- Gray code refresh counter – Uses address counters that shift by a single bit to reduce switching power in standby.

- Programmable refresh zones – Allows precise control over which blocks are refreshed, based on programmable address registers.

- Targeted housekeeping operations – Enables selective parity checking and background tasks only in required memory regions.

How It Connects To US7057960B1

- Both patents focus on reducing standby current through selective refresh and control logic.

- Each uses address-based segmentation to isolate memory sections for power management.

- Both emphasize enabling and disabling periphery circuits dynamically during background operations.

Why This Matters

This patent forms the foundation for efficient refresh strategies in dynamic memory systems. Its techniques demonstrate how to conserve power without compromising data integrity, a principle echoed in modern low-power memory architectures.

For more unusual applications of RF signals beyond device control, you might find our analysis of US6470214B1 interesting. It explores how RF waves can actually induce auditory perception.

#2. JPH02116081A

This Japanese patent, JPH02116081A, published in 1990, introduces a memory refresh technique that conserves power by targeting only active memory blocks during refresh cycles.

Source: GPS

What This Patent Introduces To The Landscape

- Block-specific refresh control – Performs refresh only on memory blocks that contain stored data, skipping unused sections.

- Power-down for inactive blocks – Sets non-data memory blocks to a wait state, reducing total current consumption.

- Address-based cell selection – Uses column and row decoders to precisely access only the required memory cells.

- System-wide power optimization – Reduces refresh power across the entire memory by isolating inactive zones.

How It Connects To US7057960B1

- Both systems divide memory arrays into sections and refresh only active areas.

- Each uses address decoding to localize refresh activity and minimize circuit engagement.

- Both aim to reduce power usage during background operations without affecting stored data.

Why This Matters

This early Japanese design highlights the value of selective memory refresh in conserving energy. Its focus on isolating active blocks aligns with the same low-power architecture principles emphasized in US7057960B1.

Did you know? System-level filters aren’t just for power; they also make old apps run on modern operating systems. US7774762B2 and Similar Software Portability Solution Patents breaks down capsule-based execution with runtime service filtering.

#3. US6343043B2

This US patent, US6343043B2, published in 2002, introduces a DRAM design that selectively skips refresh for specific memory blocks based on control input, reducing unnecessary power usage.

Source: GPS

What This Patent Introduces To The Landscape

- Refresh exclusion by address logic – Uses X pre-decoders to block refresh in sections marked as not requiring it.

- Block selection via existing pads – Inputs block-specific refresh control using standard address or data pads, eliminating the need for extra hardware.

- Self-refresh optimization – Automates refresh timing and disables unnecessary cycles through signal-driven refresh suppression.

- Low-voltage, low-power design – Tailored for mobile devices that require DRAM to operate efficiently at lower voltages.

- Integrated timing and sensing circuits – Combines timing control and sense amplification for precise bitline handling during refresh.

How It Connects To US7057960B1

- Both designs refresh only the blocks that need it, minimizing redundant power consumption.

- Each uses address-based logic to determine which memory sections remain inactive.

- Both support energy-efficient operation in battery-powered or low-voltage environments.

Why This Matters

This patent demonstrates how targeted refresh suppression and integrated control logic can significantly reduce DRAM power usage. It reinforces the approach taken in US7057960B1 to optimize memory behavior through block-aware refresh techniques.

A related shift toward activity-aware memory efficiency is explored in this patent audit of US8407411B2, which shows how DRAM frequency adapts dynamically to real workload instead of running at a fixed speed.

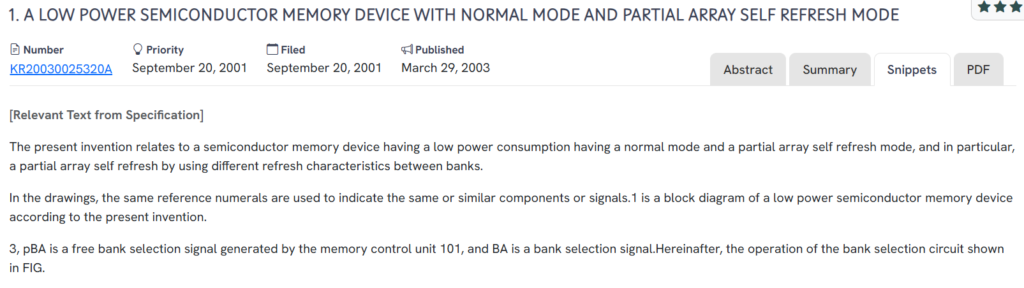

#4. KR20030025320A

This Korean patent, KR20030025320A, published in 2003, introduces a low-power semiconductor memory that operates in both standard and partial array self-refresh modes using bank-level control.

Source: GPS

What This Patent Introduces To The Landscape

- Dual refresh modes – Supports both normal operation and partial array self-refresh to reduce standby power consumption.

- Bank-specific refresh selection – Uses control signals to refresh only selected banks, avoiding unnecessary energy use in inactive banks.

- Memory control-based signaling – Implements bank selection through memory control unit outputs like pBA and BA signals.

- Asymmetric refresh characteristics – Recognizes that different banks may require different refresh strategies depending on use.

- Component-based power segmentation – Applies power-saving techniques across specific internal memory structures.

How It Connects To US7057960B1

- Both implement partial array refresh to reduce power in low-activity or standby modes.

- Each system uses targeted control logic to determine which sections of memory to refresh.

- Both focus on reducing refresh-related power draw by leveraging internal memory architecture segmentation.

Why This Matters

This patent adds further validation to the concept of bank-level refresh management for low-power memory. Its approach complements US 7,057,960 B1 by emphasizing efficient refresh control based on usage patterns and memory layout.

Fun Fact: Efficiency crosses domains. Just as US7057960B1 trims standby power, US12097189B1 trims variability in drug absorption, proving optimization is a universal IP battleground.

#5. JPH05109268A

This Japanese patent, JPH05109268A, published in 1993, introduces a dynamic memory system that reduces power usage by assigning custom refresh cycles to individual subarrays.

Source: GPS

What This Patent Introduces To The Landscape

- Subarray-specific refresh cycles – Assigns unique refresh intervals to different subarrays, avoiding uniform and excessive power use.

- Power-efficient DRAM architecture – Designed to reduce energy waste from over-refreshing inactive or low-use regions.

- Flexible refresh scheduling – Enables dynamic adjustments based on subarray activity and retention requirements.

- Access circuitry for divided memory – Features an architecture that allows for independent access and control of each subarray.

How It Connects To US7057960B1

- Both reduce unnecessary refresh operations by targeting only active or critical memory sections.

- Each design divides the memory into smaller logical units for finer control.

- Both emphasize power efficiency through intelligent refresh scheduling mechanisms.

Why This Matters

This early approach highlights the benefits of refresh customization at the subarray level. It complements US7057960B1 by reinforcing the effectiveness of fine-grained memory management in minimizing power consumption.

Note: InnoMemory US7057960B1 manages power-aware memory allocation, paralleling US7552870B2 Patent Audit, which applies decentralized efficiency models to data connectivity and bandwidth.

How To Find Related Patents Using Global Patent Search

Understanding the broader patent landscape is key when tackling power optimization, memory refresh control, or semiconductor efficiency. The Global Patent Search tool streamlines this process, helping users identify systems that reflect similar techniques in dynamic memory architecture and energy-saving logic.

To learn more about GPS capabilities, explore our full breakdown of the top features in an AI-powered patent search tool.

1. Enter the patent number into GPS: Start by entering a patent number like US7057960B1 into the GPS tool. The platform converts it into a structured query, which you can refine using terms like partial array refresh, standby current reduction, or periphery circuit control.

2. Explore conceptual snippets: Instead of comparing features claim-by-claim, GPS now delivers curated text snippets. These highlight how other systems handle selective memory refresh, bank-level control, or block-based power gating.

3. Identify related inventions: The tool reveals patents that focus on memory segmentation, background operation efficiency, or array-level logic, showing how similar power challenges have been addressed across designs.

4. Compare systems, not legal claims: Rather than relying on legal language, GPS analyzes system behavior and architectural logic. This helps users detect functional overlaps without needing to interpret complex legal texts.

5. Accelerate cross-domain insights: Whether you’re working in semiconductor design, low-power mobile architecture, or DRAM controller engineering, GPS uncovers related innovations across domains that traditional tools may miss.

With this approach, Global Patent Search provides analysts, engineers, and IP teams with a structured, concept-driven method for exploring relevant technologies and informing smarter design and patent strategies.

Disclaimer: The information provided in this article is for informational purposes only and should not be considered legal advice. The related patent references mentioned are preliminary results from the Global Patent Search tool and do not guarantee legal significance. For a comprehensive related patent analysis, we recommend conducting a detailed search using GPS or consulting a patent attorney.